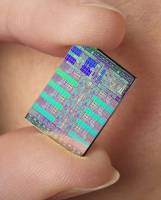

Cell / Cell BE / Enhanced Cell (Prozessor)

Im Februar 2005 haben die Firmen IBM, Sony und Toshiba den neu entwickelten Cell-Prozessor vorgestellt. Der seit 2001 in einem Gemeinschaftsprojekt entwickelte Multi-Core-Prozessor basiert auf 8 einzelnen synergetischen Prozessorkernen (SPUs), die extrem umfangreiche Fließkomma-Berechnungen verarbeiten können und über einen 64-Bit POWER-Prozessorkern gesteuert werden.

Im Februar 2005 haben die Firmen IBM, Sony und Toshiba den neu entwickelten Cell-Prozessor vorgestellt. Der seit 2001 in einem Gemeinschaftsprojekt entwickelte Multi-Core-Prozessor basiert auf 8 einzelnen synergetischen Prozessorkernen (SPUs), die extrem umfangreiche Fließkomma-Berechnungen verarbeiten können und über einen 64-Bit POWER-Prozessorkern gesteuert werden.

Die Bezeichnung Cell bezieht sich nicht auf den Hardware-Aufbau des Prozessors, sondern auf das objektorientierte Software-Design aus Befehlslogik und zu verarbeitende Daten (RISC-Befehlssatz).

Der Cell-Prozessor ist dafür ausgelegt bei hohen Taktraten hohe Datenmengen zu verarbeiten. Schon bei 4 Cell-Prozessoren mit 4 GHz Taktfrequenz würde ein Cell-Computer in die TOP500-Rangliste der schnellsten Supercomputer aufsteigen (Stand: Februar 2005).

Zehn Temperatursensoren überwachen kritische Wärmepunkte und veranlassen die Reduzierung von Takt und Spannung, wenn eine Überhitzung droht. Ziel ist es, den Cell innerhalb üblicher thermaler Bedingungen zu betreiben.

Der Nachfolger Enhanced Cell ist eine in 65-nm Ausführung mit verbesserter FPU. Um normale Speichermodule und größere Speicherkapazitäten ansprechen zu können hat er ein DDR2/3-Speicher-Interface.

Der Cell wurde hauptsächlich von Sony für die Playstation eingesetzt. Mit dem Ausstieg von IBM aus diesem Projekt, ist davon auszugehen, dass Sony auf den Cell zukünftig verzichten wird und statt dessen auf einen Prozessor von AMD, vielleicht auch Intel setzt.

Besonderheiten des Cell

- Multi-Core/Thread-Architektur

- Unterstützung multipler Betriebssysteme

- hohe Bandbreite zum Arbeitsspeicher und Peripherie

- flexibles Schnittstellen-Interface

- Resourcenmanagement für Echtzeitanwendungen

Die Möglichkeiten der Cell Broadband Engine sind noch nicht vollständig ausgeschöpft.

Architektur: Cell Broadband Engine / Cell BE

In der Cell BE sind viele alte Architekturen enthalten, die mit vielen neuen Ansätzen geschickt zusammengeführt wurden. Zum Beispiel Multi-Threading mit parallel arbeitenden Kernen und einer sehr schnellen Kommunikationsschnittstellen zwischen den Elementen.

In der Hauptsache basiert die Architektur des Cell auf der 64-Bit IBM-Power5-Architektur. Man nennt sie Cell Broadband Engine, kurz Cell BE. Die einzelnen CPU-Kerne werden Synergistic Processing Element (SPE) genannt. Darin enthalten ist die Synergistic Processing Unit (SPU), eine mehrfach parallel arbeitenden Recheneinheit (SPX) und einen lokalen Speicher (LS) von 256 kByte hat. Die SXU besteht aus einer Fließkomma- und Integer-Einheit, sowie Permutations- und Lese/Schreib-Einheit. Über ihren DMA (Direct Memory Access) haben die SPEs Zugriff auf den Hauptspeicher, der Memory Management Unit (MMU) und dem Bus-Interface. Zusammen bilden sie die Synergistic Memory Flow Controller Unit (SMF oder MFC).

Gesteuert werden die SPEs von einem vereinfachten 64-Bit-Power5-Prozessor (PowerPC Processing Element, PPE). Er besteht aus 2 x 32 kByte L1-Cache, 128 Registern, einer Fließkommaeinheit, einer VMX-Erweiterung für Gleitkomma-Berechnungen und einem Dual-Thread-SMT, der mit Intels HyperThreading vergleichbar ist. Der Power-Prozessor verfügt über eine 11-stufige Pipeline mit einer In-Order-Struktur. Mittels der 8 SPEs führt der Cell-Prozessor bis zu 8 Befehlsfolgen gleichzeitig aus. Wobei der PPE nicht die Rechenleistung des Cell liefert. Dafür sind die SPEs zuständig, die viel schneller rechnen, als der PPE.

Der Cell enthält insgesamt 2,5 MByte Speicher. 512 kByte entfallen auf die Steuer-CPU (PPE), der Rest mit jeweils 256 kByte auf die 8 SPEs. Über eine bidirektionale Verbindung greift eine SPE direkt auf den lokalen Arbeitsspeicher zu. Ganz ohne Cache-Hierarchie.

Die interne Verbindung zwischen den Kernen, dem Speicher und I/O-Controller wird über einen Ring (Element Interface Bus, EIB) realisiert. Dieser Systembus arbeitet mit halbem Systemtakt. Über vier Ringe (je 2 pro Richtung) werden die insgesamt 12 Elemente mit 128 Bit miteinander verbunden. Jedes Element ist bidirektional mit zwei Ports (je 128 Bit) an den Ringen angeschlossen. Der Systembus überträgt 96 Byte pro Taktzyklus, wobei die Bandbreite einer Prozessoreinheit auf 16 Byte pro Taktzyklus beschränkt ist. Bei einem Bustakt von 1,6 GHz können je Richtung 25,6 GByte/s übertragen werden. Da die Laufzeiten je nach Lage im Bus unterschiedlich sind, variiert die Bandbreite je nach Ziel-Element zwischen 78 und 197 GByte/s. Die theoretische Gesamtbandbreite des EIB ist mit 204 GByte/s angegeben.

Der Datenaustausch zwischen PPE, SPEs, dem Speicher- und Eingabe-Ausgabe-Controller ist in einem Protokoll festgelegt. Der Speicher-Controller hat die höchste Priorität. Alle anderen Einheiten haben die gleich Priorität.

Im Cell ist ein Speichercontroller (Memory Interface Controller, MIC) integriert, der über das Dual Channel XDR von Rambus mit 72 Bit an den Arbeitsspeicher angebunden ist. Diese Schnittstelle arbeitet mit einer Frequenz von 3,2 GHz und überträgt mit zwei Kanälen 25 GByte/s. Als Verbindung zur Peripherie dient der Flex I/O, ebenfalls von Rambus. Sieben 8-Bit breite Verbindungen sind für die ausgehenden Daten zuständig. Fünf weitere 8 Bit breite Verbindungen sind für die eingehenden Daten zuständig. Jede Verbindung hat eine Übertragungsrate von 6,4 GByte/s. Insgesamt entsteht so eine Schnittstelle mit 76,8 Gyte/s zur Peripherie. Zum internen Bus ist der Controller mit 2_16 Byte pro Taktzyklus verbunden.

Anwendungen

Der Cell ist für rechenintensive und breitbandige Anwendungen, wie Multimedia, Computerspiele, Videos und andere Formen digitaler Inhalte optimiert. Zum Beispiel wird der Cell in Sonys Spielekonsole Playstation 3 als Hauptprozessor verwendet.