Pullup-, Pulldown-Widerstand

Massnahmen zur Entstörung bei langer Leitung

Openkollektor - Wired-OR - Latchup-Risiken

Was ist ein Pullup- und ein Pulldown-Widerstand?

Pull heisst bekanntlich ziehen, Up heisst rauf und Down heisst runter. Ein Pullup-Widerstand zieht also etwas hinauf und ein Pulldown-Widerstand zieht etwas hinunter. Genau so einfach ist es. Der eine zieht die elektrische Spannung hinauf und der andere zieht sie hinunter. Das Hinaufziehen geht dabei meist bis zum Betriebsspannungswert +Ub und das Hinunterziehen hinunter auf GND, oder im Falle einer symmetrischen Betriebsspannung mit ±Ub auf -Ub. Damit wäre eigentlich schon alles geklärt, wenn es nicht etwas komplizierter wäre...

Es gibt zwei Möglichkeiten einen Taster mit einem logischen Gatter zu

verbinden. Will man dafür sorgen, dass der Eingangspin logisch LOW

erhält, wenn die Taste gedrückt wird, so gilt Teilbild 1.1. Der Kontakt

liegt zwischen dem Eingang des Gatters und GND. Es kann anstelle des

Tasters auch ein Schalter sein. Der Pullup-Widerstand liegt zwischen dem

Eingang und +Ub. Beim Öffnen des Tasters zieht der Pullup-Widerstand die

Spannung am Eingang hoch bis zum Betriebsspannungswert +Ub, was logisch

HIGH entspricht. Das Gatter selbst ist selbstverständlich mit der selben

Betriebsspannung +Ub und GND gespiesen und das gilt für alle folgenden

Bilder, wo die Speisung nicht speziell gekennzeichnet ist.

Will man dafür sorgen, dass der Eingang logisch HIGH erhält, wenn die

Taste gedrückt wird, gilt Teilbild 1.2. Der Kontakt liegt zwischen dem

Eingang und +Ub. Der Pulldown-Widerstand liegt zwischen dem Eingang und

GND. Beim Öffnen des Kontaktes zieht der Pulldown-Widerstand die

Spannung am Eingang hinunter auf GND, was logisch LOW entspricht. LOW

oder HIGH wird am Eingang nur dann per Widerstand erreicht, wenn es ein

CMOS-Eingang ist, weil dieser extrem hochohmig ist. Bei TTL-Bausteinen

ist dies nicht der Fall, wie wir noch sehen werden.

Es werden hier Eingänge von NAND-Gattern gezeigt. Natürlich können dies

auch andere digitale Eingänge sein, wie z.B bei einem Flipflop, Zähler

oder Schieberegister. Bei der Anwendung von Pullup- und

Pulldown-Widerständen geht es ganz einfach immer darum, dass bei einem

offenen Kontakt der korrekte logische Eingangspegel garantiert ist.

Darauf werden wir noch näher eingehen.

Ein Pullup- oder Pulldownwiderstand kommt auch bei einer Steuerung

mittels Transistor zum Einsatz, der ähnlich einem Schalter dem Ein- und

Ausschalten dient. In diesem Fall ist der Pullup- oder

Pulldownwiderstand auch ein Kollektorwiderstand. Ein Widerstand im

Kollektorkreis einer Schalt-Transistorstufe, dargestellt in den

Teilbildern 1.3 und 1.4. Häufig findet man die Schaltung in Teilbild

1.3. Ein NPN-Transistor in der Funktion eines Openkollektor-Ausganges,

integriert z.B. in einem

Optokoppler.

Siehe Skizze unter "Gleichstrom-Übertragungsverhältnis".

Das RS-Flipflop

Das RS-Flipflop ist eine typische Anwendung für Pullup- oder Pulldown-Widerstände. Immer dann wenn mechanische Kontakte - hier Taster - zur Anwendung kommen, sind diese Pullup- oder Pulldown-Widerstände notwendig, um den Logikpegel bei offenem Kontakt sicher zu stellen. Sollte der Leser nicht wissen was ein RS-Flipflop ist, so mache er sich bitte schlau in Patrick Schnabels RS-Flipflop-Grundkurs in:

Auf dieser Seite wird je ein RS-Flipflop mit zwei NAND- und zwei NOR-Gattern vorgestellt. Bild 2 (hier) illustriert zusätzlich die Pullup- und Pulldown-Widerstände. Die Dimensionierung dieser Widerstände wird weiter unten thematisiert.

Der prellfreie Schalter mit RS-Flipflop

Der prellfreie Taster oder prellfreie Schalter, zeigt Bild 3 in den

Ausführungen mit einem NAND-RS- und einem NOR-RS-Flipflop. Dies ist eine

sehr typische Anwendung für RS-Flipflops mit Pullup- und

Pulldown-Widerständen. Nachteilig ist, dass man einen Umtaster, bzw.

Umschalter, einsetzen muss. Einen prellfreien Taster oder Schalter mit

nur einem Arbeitskontakt muss mit einem Monoflop realisiert werden,

dessen Impulsdauer grösser ist als die Prellzeit.

RS-Flipflop entstören: Wie man ein RS-Flipflop in einer stark

EMV-verstörten Umgebung, z.B. in einer Steuerungsanwendung im

230-VAC-Bereich, desensibilisiert, zeigt folgender Elektronik-Minikurs

(Bilder 4, 5 und 6):

TTL war früher, (H)CMOS ist heute

Die Transistor-Transistor-Logik (TTL) wird hier bloss noch vollständigkeitshalber thematisiert. Für neue Projekte werden nicht mehr Standard-TTL, LS-TTL oder ALS-TTL eingesetzt. Wer trotzdem mehr zu diesen Bausteinen, jedoch auch einiges über (H)CMOS erfahren möchte, empfehle ich meinen Artikel aus dem Jahre 1992 in:

Standard-TTL und die Pullup- und Pulldown-Widerstände

Bild 4 zeigt zwei Standard-TTL-Eingänge. Teilbild 4.1 mit einem Pullup-

und Teilbild 4.2 mit einem Pulldown-Widerstand beschaltet.

Betrachten wir zuerst Teilbild 4.1. Wie gross muss Rpu (Resistor-pullup)

sein? Im Prinzip kann er beinahe beliebig gross dimensioniert werden

oder man könnte auf ihn auch ganz verzichten. Bei offenem Eingang

fliesst ein T1-Basisstrom, begrenzt durch R1, über die

T1-Basis-Kollektor-Diode in die Basis von T2. T2 und T4 leiten und T3

ist offen. Der Ausgang des TTL-NAND-Gatter liegt damit auf logisch LOW.

Wenn Rpu eingesetzt wird, steigt die Spannung am Eingang auf die

Betriebsspannung von +5 VDC. Damit wird der Störabstand des NAND-Gate

verbessert, was sich besonders bei langen Leitungen am Eingang

störsicherer auswirkt. Der Emitter-Kollektor-Sperrstrom des T1 ist so

gering, dass Rpu relativ hochohmig gewählt werden kann. 100 k-Ohm sind

zwar möglich, empfohlen werden jedoch Werte zwischen 5 und 10 k-Ohm. Zu

hohe Rpu-Werte erhöhen durch Einkopplung mittels parasitärer

Leitungskapazitäten die Störempfindlichkeit.

Betrachten wir jetzt das Teilbild 4.2. Wie gross muss Rpd

(Resistor-pulldown) sein? Hier fliesst ein T1-Basisstrom über einen der

beiden T1-Emitter und Rpd nach GND. Aus T1 fliesst kein Kollektorstrom

wenn einer der beiden Emitter von T1 auf GND-Pegel liegt, weil die Basis

von T2 über die leitende Kollektor-Emitterstrecke von T1 ebenfalls auf

GND gezogen wird. Der Basisstrom Ib von T1 entspricht dem Emitterstrom

Ie von T1.

Dieser Strom erzeugt in Rpd einen Spannungsabfall und dieser darf gemäss

Datenblatt 0.8 VDC nicht überschreiten. Der durch R1 begrenzte Strom

liegt bei maximal 1.1 mA. Damit die Spannung von 0.8 VDC am Eingang

nicht überschritten wird, darf Rpd nicht grösser als 720 Ohm sein. Es

werden in der Praxis allerdings Werte unter 500 Ohm, in der Regel ein

Widerstand von 390 Ohm, empfohlen.

Bei der Anwendung von Pulldown-Widerständen zeigt sich bei

Standard-TTL-Schaltungen sogleich ein gravierender Nachteil: Der Strom

ist bei geschlossenem Taster- oder Schaltkontakt relativ gross. Bei

einem Rpd-Wert von 390 Ohm resultiert ein Strom von 13 mA. Im Gegensatz

dazu erzeugt ein Rpu-Wert von 10 k-Ohm bei geschlossenem Kontakt bloss

0.5 mA. Besonders dann wenn eine grosse Menge von Schaltern zum

Einsatz kommt, zeigt sich der Vorteil beim Einsatz von

Pullup-Widerständen.

LS-TTL und die Pullup- und Pulldown-Widerstände

Auch diese Logik ist sehr alt (LS=Lowpower-Schottky) und es gab auch

längst die ALS-TTLs (A = Advanced) welche die LS-TTLs verdrängte. Diese

ALS-TTL-Bauseine sind schneller als die LS-TTLs, benötigen jedoch

unwesentlich mehr Leistung. Aber uns interessiert hier nur die

Angelegenheit der Pullup- und Pulldown-Widerstände.

Betrachten wir zunächst das Schaltbild in Teilbild 5.1. Schottky-Dioden

schalten wesentlicher schneller um vom sperrenden in den leitenden

Zustand und umgekehrt. Die Durchfluss-Schwellenspannung beträgt nur etwa

0.3 bis 0.4 VDC, während es bei herkömmlichen Siliziumdioden etwa 0.6

bis 0.8 VDC sind. Betreffs Rpu gelten etwa die selben Überlegungen wie

zur Teilschaltung 4.1. Gleichgültig wie hoch Rpu ist, die Diode liegt in

Sperrrichtung und es fliesst bloss ein irrelevant geringer Sperrstrom.

Trotzdem sollte man es mit dem Wert des Rpu, aus dem Grund wie bereits

beschrieben, nicht übertreiben.

In Teilbild 5.2 wirkt Rpd und es fliesst ein Strom durch den

stromlimitierenden Widerstand R1, Schottky-Diode D1 und Rpd nach GND. R1

ist in LS-TTL-Schaltungen allerding fünf mal grösser als in

Standard-TTL-Schaltungen. Daher darf Rpd mit 1.8 k-Ohm auch etwa fünf

mal grösser sein.

Was ist ein Schottky-Transistor

Dies ist im Grunde nichts anderes als ein ganz normaler

schnellschaltender NPN-Transistor kombiniert mit einer Schottky-Diode

zwischen Basis und Kollektor. Wozu soll denn das dienen? Ganz einfach,

es wird verhindert, dass der Basisstrom des Transistors unnötig gross

wird. Sobald beim Anstieg des Basisstromes der Kollektorstrom in

Funktion des Stromverstärkungsfaktores zunimmt, sinkt die

Kollektor-Emitter-Spannung. Wird diese Spannung niedriger als die

Flussspannung der Schottky-Diode, fliesst ein Teil des Stromes anstatt

zur Basis über die Diode zum Kollektor. Dadurch wird wirksam verhindert,

dass der Transistor in die Sättigung gesteuert wird. So müssen nach

Wegfall des Basisstromes weniger Ladungsträger aus der Basis

"ausgeräumt" werden und der Transistor schaltet schneller aus.

Man kann diesen Trick auch mit herkömmlichen Siliziumdioden realisieren.

Allerdings arbeitet die Schaltung dann langsamer und die minimale

Kollektor-Emitter-Spannung ist höher.

Pullup- und Pulldown-Widerstände an CMOS-Eingängen

Offene TTL-Eingänge sind prinzipiell logisch HIGH, auch wenn dies nicht

ganz unproblematisch ist, wie wir weiter oben gelesen haben. Wie sieht

dies mit CMOS-Eingängen aus? Die Oxydschicht zwischen Gate und Source

ist ein perfekter Isolator. Ein Eingangswiderstand von 1012

Ohm ist selbstverständlich. Was hindert uns also für Rpu und Rpd Werte

im M-Ohm-Bereich zu wählen? Im Grunde nichts, wenn da nicht einige

Kriterien aus der Praxis zu berücksichtigen sind. Wenn durch

Verschmutzung Kriechstrecken entstehen, nimmt an dieser Strecke der

Widerstand ab. Passiert dies zwischen den Kontakten eines Schalters oder

Tasters, dann haben wir einen Spannungsteiler der entweder aus Rpu und

dem offenen Kontaktübergangswiderstand (Teilbild 7.1) oder aus Rpd und

dem offenen Kontaktübergangswiderstand (Teilbild 7.2) besteht. Dadurch

wäre die korrekte logische Eingangsspannung nicht mehr gewährleistet.

Betreffs Grösse von Rpu und Rpd kommt es ganz auf die Anwendung an. Im

Normalfall eignen sich gut Werte von 10 bis einigen 100 k-Ohm. Im

nächsten Kapitel befassen wir uns mit dem Störrisiko bei langen

Leitungen zwischen der Kontaktstelle und der Elektronik und wir

überlegen uns was im Falle des Batteriebetriebes zu beachten ist. Diese

Situation weicht etwas vom Normalfall ab.

Störsichere Gate-Eingangsschaltung eines CMOS-IC

Wie funktioniert diese Schaltung? R1 ist der Pullup-Widerstand. Beim

Öffnen des Kontaktes und bei offenem Kontakt wirkt die Zeikonstante R1*C

mit 10 ms. Bei diesem Wert können selbst massive kapazitive

Einkopplungen auf die lange Leitung von niederfrequenten Signalen kaum

stören. Hochfrequente Störsignale haben eh keine Chance, vorausgesetzt

allerdings, dass C kein Wickel- sondern ein Keramikkondensator ist.

Dieser hat eine speziell niedrige parasitäre Eigeninduktivität.

Man sollte hier auf eine relativ grosse R1*C-Zeitkonstante achten, denn

bei einem hochohmigen Eingang und bei der Verwendung einer sehr langen

Leitung, können auch mittel- und niederfrequente Einkopplungen stören.

Bei geschlossenem Tasten- oder Schalterkontakt ist der Eingang

niederohmig. Der sehr niedrige Widerstand, bestehend aus Kontakt und

Leitung, dominiert. Wir dürfen aber nicht vergessen, dass die Leitung

auch eine gewisse Induktivität besitzt. Sie ist eine parasitäre Spule

mit einer Windung. Dies ist, extrem betrachtet, auch dann der Fall wenn

eine parallele Zweidrahtleitung verwendet wird. Allerdings ist dann die

Antennenwirkung sehr gering. Wollen wir aber auch gleich diesem Problem

vorbeugen, so schalten wir in Serie zum Eingang R2 mit einem Wert von

z.B. 10 k-Ohm. R2 erzeugt mit C eine Zeitkonstante von 0.33 ms. Dies

dürfte ausreichen, da bei geschlossenem Kontakt eine niedrige Impedanz

vorliegt, bei der nur hochfrequente bzw. steilflankige Einkopplungen

überhaupt wirksam werden können. Der passive Tiefpass aus R2*C dämpft

dies wirksam. R2 hat aber noch einen anderen Zweck. Ohne R2 bildet sich

aus der Leitungsinduktivität und C ein eher schwach gedämpfter

Schwingkreis, der durch eine steilflankige Störeinkopplung angeregt

werden könnte. Die daraus resulierende Amplitude könnte zu einer

Fehltriggerung des nachgeschalteten Systemes führen. Mit R2 erreicht man

eine wirksame Dämpfung dieses parasitären Schwingkreises.

Aber wozu braucht es jetzt noch R3, neigt der aufmerksame Leser sich zu

fragen. Das ist ganz einfach: Nehmen wir an, es kommt auf der langen

Leitung zu einem Überspannungsimpuls, dann könnte der Stromimpuls durch

die Schutzdioden D1 und D2 kurzzeitig so gross werden, dass ohne R3 die

ebenso kurzzeitig erhöhte Durchfluss-Spannung der IC-internen

Schutzdioden überschritten wird. Die Folge davon wäre ein Latchup-Effekt

des CMOS-IC. Dieser führt bekannterweise zum Kurzschluss durch die

Zündung eines IC-internen parasitären Thyristors und zerstört das IC.

Mit R3, der durchaus auch grösser gewählt werden kann, wird der

Eingangsstrom ins Gate, im Falle einer Eingangsspannung unterhalb von

GND oder oberhalb von +Ub, so weit begrenzt, dass der Latchup-Effekt

sicher nicht auftreten kann. Sicher, weil die Eingänge der CMOS- und

HC(T)MOS-Familien bereits integrierte Widerstands-Dioden-Netzwerke

enthalten, die jedoch möglichst nicht überstrapaziert werden sollen.

Daher lohnt es sich stets vor dem Eingang zusätzliche Massnahmen zu

treffen, wie dies in Bild 8 gezeigt wird.

Betreffs Überspannungsschutz an elektronisch sensiblen Eingängen

empfiehlt sich auch der Elektronik-Minikurs

Überspannungsschutz von

empfindlichen Verstärkereingängen. Es geht dabei zwar um Opamps,

jedoch das Prinzip ist das selbe. R2 in Bild 8 hat die selbe Bedeutung

wie R3 hier zufällig ebenfalls in Bild 8.

Es sei noch vollständigkeitshalber darauf hingewiesen, dass die

Massnahme in Bild 8 als Überspannungsspannungsschutz gegen eine starke

elektrostatische Entladung, induziert z.B. durch eine indirekte

Blitzentladung in der Nähe, nicht ausreicht!

Schmitt-Trigger: Wozu werden in Bild 8 für das NAND-Gate

Schmitt-Trigger-Versionen z.B. CD4093, 74HC132 und 74HCT132 empfohlen?

Vor allem beim Öffnen des Kontaktes ist die Flankensteilheit am

Gate-Eingang, wegen der hohen Zeitkonstante von 10 ms, sehr niedrig.

Aber auch beim Schliessen des Kontaktes mit 0.33 ms ist der Wert noch

immer zu niedrig. Dies kann, wenn das Gate keine

Schmitt-Trigger-Funktion aufweist, während des Schaltvorganges zu

kurzzeitigen unkontrollierten Schwingungen am Ausgang des Gate kommen.

Wenn die nachfolgende Schaltung ein einfaches RS-Flipflop ist, macht das

keine Probleme, weil dieses Flipflop schliesslich nur einmal gesetzt

oder einmal zurückgesetzt werden kann. Anders sieht es aus, wenn ein

Toggle-Flipflop, ein Counter oder Schieberegister mit dem fernen Taster

getaktet werden soll. Dann erzeugen die kurzzeitigen Schwingungen

sogleich mehrfaches Takten und die Folge davon sind falsche digitale

Werte. Bei solch digitalen Schaltkreisen darf man allerdings nicht

vergessen, dass eine einfache Taster-Schaltung nicht genügt. Es wird

eine prellfreie Tasterfunktion, z.B. eine solche wie Bild 3 zeigt,

benötigt.

Pullup-, Pulldown-Widerstand und Batteriebetrieb

Eine CMOS-Schaltung braucht im Ruhezustand bekanntlich keine

signifikante Leistung. Man braucht also nur dafür zu sorgen, dass eine

CMOS-Schaltung keine Taktfrequenz erhält, und die Schaltung braucht

nicht extra per Hauptschalter von der Batterie getrennt zu werden. Wie

aber sieht es beim Gebrauch von Pullup- und Pulldown-Widerständen aus?

Wenn der Kontakt im Auszustand gerantiert offen ist, gibt es kein

Problem, denn wenn die CMOS-Schaltung unter Batteriespannung steht,

fliesst kein Gatestrom. Bei geschlossenem Kontakt fliesst allerdings ein

Strom durch den Pullup- oder Pulldown-Widerstand. Kann man den

geschlossenen Kontakt nicht vermeiden, muss man dafür sorgen, dass der

Pullup- oder Pulldown-Widerstand sehr hochohmig ist und man muss

staubgeschützte Kontakte und Anschlüsse verwenden, damit der Widerstand

zwischen den Kontakten um Grössenordnungen hochohmiger bleibt, als der

Pullup- oder Pulldownwiderstand, wenn der Kontakt geöffnet ist.

Angenommen die CMOS-Schaltung wird aus einer 9V-Block-Batterie betrieben

und man wählt einen Pullup- oder Pulldown-Widerstand von 1 M-Ohm,

fliesst ein Strom von 9 µA bei geschlossenem Kontakt. Bei einer

Batterie-Kapazität von 400 mAh (soviel hat etwa eine

Alkali-Mangan-9V-Blockbatterie), beträgt die Lebensdauer der Batterie,

wenn die Schaltung selbst nie in Betrieb ist, etwa 44'000 Stunden und

das sind 5 Jahre. Dies ist in der Regel mehr als die Lagerfähigkeit

einer solchen Batterie bei Raumtemperatur. Der Selbstentladedestrom der

Batterie ist grösser. Ein Pullup- oder Pulldown-Widerstand von 1 M-Ohm

wäre also sicher zumutbar, er dürfte allerdings auch halb so gross sein.

Elektrostatischer Einfluss auf ein offenes CMOS-Gate

Was passiert wenn ein TTL-Eingang offen ist? Nichts. Er ist auf logisch

HIGH definiert. Einzig der Störabstand ist veringert, wenn am Eingang

eine Leiterbahn oder eine Leitung angeschlossen ist. Was passiert aber

wenn ein CMOS-Eingang offen ist? Viel!

Der Eingang ist extrem hochohmig. Ohne externe Einflüsse ergibt sich die

Eingangsspannung aus den ebenso extrem hochohmigen Übergangswiderständen

zwischen Anschlusspin und GND und Anschlusspin und +Ub. Liegt die

Spannung beim halben Wert von +Ub kommt die CMOS-Schaltung in den

leitenden Zustand, weil der N-Kanal- und der P-Kanal-MOSFET von der

Endstufe gleichzeitig dauernd leiten. Der Strom liegt bei der

CD4xxx-IC-Familie bei einigen Milliampere pro CMOS-Gatter. Es leuchtet

natürlich ein, dass ein solch offener CMOS-Eingang den Betrieb der

Schaltung massiv stört. Facit: Man muss immer ein Pulldown- oder ein

Pullup-Widerstand einsetzen, der, wie wir jetzt wissen, unter bestimmten

Voraussetzungen auch relativ hochohmig sein darf.

Ein offener CMOS-Eingang ist aber auch der Willkür freier elektrischer

Felder ausgesetzt. Dazu kann man sich mit Bild 9 selbst ein

eindrückliches aber einfaches Experiment aufbauen:

Wenn der Eingang des CMOS-NAND-Gatters auf LOW gesetzt ist, liegt sein

Ausgang auf HIGH. Es fliesst ein Strom durch in die Basis des

Transistors T der verstärkt wird. Daher fliesst ein Emitterstrom und die

LED leuchtet. R begrenzt den LED-Strom. Nun lassen wir den Eingang

offen, schliessen lediglich einen etwa 10 cm langen Draht an den Pin und

sorgen dafür, dass er frei in der Luft liegt. Nun kämmen wir mit einem

Kunstoffkamm unser Haar, das trocken sein muss, oder wir reiben einen

Kunststoffstab, z.B. Plexiglas oder PVC, an einem trockenen Wolltuch.

Wir führen den elektrostatisch geladenen Kamm oder Stab in die Nähe des

freistehenden Drahtes. Eine Distanz von fünf bis zehn Zentimeter genügt.

Nun bewegen wir den Kamm oder den Stab leicht hin- und her in Richtung

des Drahtes und beobachten wie im selben Rythmus die LED aufleuchtet und

erlischt. Bewegen wir den Kamm oder den Stab ganz langsam, können wir

sogar die Helligkeit der LED etwas steuern. Dies braucht allerdings

etwas Übung.

Für ein besonders wirksames Experiment im Schulzimmer kann man anstelle

des bipolaren Kleintransistors T und einer LED einen Power-MOSFET

verwenden und damit eine 12-Volt-Autobirne ansteuern. Man braucht dazu

allerdings eine 12VDC-Spannungsquelle welche gut 4 Ampere liefert, z.B.

ein kleiner Bleiakku.

Unbenutzte Logik-Eingänge

Pullup/Pulldown-Widerstände, ja oder nein: In einem Thread im ELKO-Forum wurde zum Thema unbenutzte CMOS-Eingänge am Beispiel eines MOS-Zählers diskutiert. Dies veranlasste mich diesen Elektronik-Minikurs mit diesem Thema abzurunden.

Es gilt generell für TTL und CMOS-ICs, dass unbenutzte Eingänge auf HIGH

oder LOW geschaltet werden, je nachdem welchen Einfluss sie haben

sollen. Teilbild 10.1 zeigt die Schaltung A mit zwei logischen

Ausgängen, die mit einem NAND-Gate zu verknüpfen sind. Da nur ein

unbenutztes NAND-Gate mit drei Eingängen zur Verfügung steht, muss der

dritte unbenutzte Eingang so beschaltet sein, dass dieser die logische

Verknüpfung des beiden A-Ausgänge nicht beeinflusst. Dies ist der Fall,

wenn der dritte Eingang auf HIGH gesetzt ist. Im Fall von Teilbild 10.2

ist es gerade umgekehrt. Der dritte Eingang muss auf GND gesetzt sein,

damit die NOR-Funktion mit nur zwei Eingängen unbeeinflusst bleibt.

Wie wir bereits wissen muss ein TTL-Eingang, der logisch HIGH

entsprechen muss, nicht unbedingt mit HIGH verbunden sein. Trotzdem

sollte man es tun wegen dem besseren Störabstand. Bei CMOS darf kein

Eingang offen sein (Grund: siehe weiter oben). Warum sind keine Pullup-

und Pulldown-Widerstände notwendig, wie dies die Teilbilder 10.3 und

10.4 zeigen? Ganz einfach, weder im Betriebszustand, noch in der Ein-

und Ausschaltphase ist es möglich, dass die Eingangsspannung des

unbenutzten Einganges negativer sein kann als GND und ebenso wenig

positiver sein kann als +Ub. Es muss kein Strom in das Gate hinein

begrenzt werden. Man beachte in den Datenblättern die sogenannten

Worstcase-Daten. Da liest man in der Regel, dass die Eingangsspannung

nicht positiver als +Ub plus 0.5 V und nicht negativer als GND minus 0.5

V sein darf. Dieses Problem kann hier gar nie eintreten.

Die Teilbilder 10.5 bis 10.8 zeigen die selbe Situation, wenn digitale

CMOS-Schaltkreise symmetrisch mit ±Ub gspiesen werden. In diesem Fall

gilt -Ub für den LOW-Pegel und nicht GND. Der GND-Pegel liegt in der

Mitte von +Ub und -Ub, wenn +Ub und -Ub gleich gross sind. Diese

Logiksituation kommt oft dann vor, wenn eine komplexe Schaltung aus

analogen Schaltkreisen besteht, welche symmetrisch mit ±Ub gespiesen

wird und von digitalen CMOS-Schaltkreisen gesteuert werden. Allerdings

gibt es da auch Interfaceschaltkreise, welche GND-bezogene

Logik-Eingänge und ausgangsseitig nicht potenzialbezogene analoge

CMOS-Schalter enthalten, die in der Lage sind analoge Spannungen

innerhalb der positiven und negativen Betriebsspannung zu schalten. Eine

praktische Anwendung gibt es im Elektronik-Minikurs zum Thema

SC-Tiefpassfilter-Einheit mit

umschaltbaren Grenzfrequenzen.

Man betrachte dazu Bild 5 im Kapitel "Umschaltbare fixe

Grenzfrequenzen (Schema)". Da werden analoge aktive Tiefpassfilter,

welche mit ±5 VDC gespiesen werden, von digital gesteuerten

Analogschaltern (IC:B1,B2,B3,E1,E2,E3) von Logikpegeln mit 5V (HIGH) und

GND-Pegel (LOW) umgeschaltet. Diese Analogswitches vom Typ

DG202B

enthalten die entsprechend notwendigen Interfacefunktionen. Siehe

Blockschema Figure 1 und beachte den Block

"Level Sift/Drive".

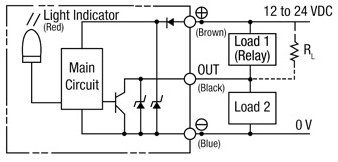

Openkollektor schaltet CMOS- oder TTL-Digital-IC

Quelle: Digi-Key: Sensor-Solutions

Quelle: Digi-Key: Sensor-Solutions

Diese Prinzipschaltung eines eigentlichen Lichtsensors mit Schaltausgang dient als Anschauungsmaterial zu diesem Kapitel. Der Lichtempfänger - im vorliegenden Fall ist es infrarot - erzeugt einen lichtabhängigen Strom. Dieser Strom (die Lichtstärke) wird durch eine Triggerschaltung in Main-Circuit ausgewertet. Oberhalb eines gewissen Pegels erhält der NPN-Transistor Basisstrom. Dies ermöglicht einen Kollektorstrom, ausgehend von einer positiven Betriebsspannung, der durch den Lastwiderstand RL (z.B. ein Relais) zum Kollektor des Transistor fliesst. Der leitende Transistor ermöglich den Stromfluss vom Kollektor zum Emitter nach GND. Uns interessiert zunächst die Pullup-, bzw. die Wired-OR-Funktion und betrachten Bild 11:

Es gibt verschiedene Sensorschaltungen mit Logik-Ausgängen, welche mit

einem NPN-Transistor in Emitterschaltung mit offenem Kollektor

ausgerüstet sind. Eine Openkollektor-Schaltung hat den Vorteil der

sogenannten Wired-OR-Verknüpfung. Der Vorteil besteht darin, dass man

sehr viele solcher Sensoren mit einer Wired-OR-Verknüpfung parallel mit

einem einzigen Pullup-Widerstand (Rpu) schalten kann. Dies erspart eine

Menge Logik-Gatter.

Teilbild 11.1 zeigt eine beliebige Anzahl von Lichtsensoren (SENSOR-1

bis SENSOR-n). Die Openkollektor-Ausgänge (Ua1 bis Uan) sind miteinander

verbunden und mittels eines gemeinsamen Pullup-Widerstand Rpu mit einer

positiven Spannung +Ub2 verbunden. +Ub2 kann dem Wert der

Betriebsspannung +Ub1 entsprechen oder jeden andern Spannungswert

zwischen etwa +1 VDC bis etwas weniger haben, als die maximal zulässige

Kollektor-Emitter-Spannung des Openkollektor-Transistors des Sensors

zulässt (Datenblatt). Wenn einer der Sensor-Transistoren einschaltet und

Uax auf LOW (GND-Pegel) geht, geht Ua ebenfalls auf LOW und ein Alarm

wird beispielsweise ausgelöst. Der HIGH-Pegel (kein Sensor ist aktiv)

entspricht, an Ua unbelastet, der Spannung +Ub2.

Damit man diese Funktionsweise als wired-OR bezeichnen kann, gilt die

negative Logik. In der positiven Logik kodiert der High-Pegel den

Binärwert 1 (HIGH) und der Low-Pegel den Binärwert 0 (LOW). In negativer

Logik stellt der High-Pegel die 0 (LOW) und der Low-Pegel die 1 (HIGH)

dar. Genau das trifft hier in Teilbild 11.1 zu. Teilbild 11.2 zeigt ein

AND-Gatter mit n Eingängen. In negativer Logik ist es ein OR-Gatter mit

n Eingängen. Wenn auch nur ein Eingang auf LOW gesetzt wird, setzt Ua

auf ebenfalls auf LOW. Nur dann wenn alle Eingänge auf HIGH sind, ist

auch Ua auch HIGH. Teilbild 11.3 zeigt die selbe Funktionseigenschaft

aufgeteilt in vier AND-Gatter im Sinne der positiven und als OR-Gatter

im Sinne der negativen Logik. Teilbild 11.4 wiederholt das selbe als

passive wired-OR-Schaltung mit n Eingängen und einem Pullup-Widerstand.

Die Schalter sind die Transistoren in Teilbild 11.1. So erkennt man

leicht, dass diese Schaltung den geringsten Aufwand aufweist.

Zusätzliche Informationen im ELKO findet man im

Digitaltechnik-Grundlagenkurs

Logik-Pegel

Die selbe passive Methode wiederholt in Teilbild 12.1 ist allerdings mit einem Nachteil behaftet, wenn höhere Frequenzen im Spiel sind: Der Quellwiderstand an Ua ist beim HIGH-Pegel alleine durch den Pullup-Widerstand Rpu definiert. Ist ein Schalter (Transistor) eingeschaltet, definiert der sehr niederohmige Kontakt-Widerstand den Quellwiderstand an Ua. Daraus folgt, dass ansteigende Schaltflanken an Ua immer weniger steil sind, als die fallenden, denn aufgeladen wird die unvermeidliche parasitäre Kapazität Cpar (Leiterbahn, Kabel, etc.) an Ua immer langsamer, als sie entladen wird.

Betriebsspannung des Sensor höher als die der Steuerung: Dazu

kommt noch, dass die Betriebsspannung der Steuerung von aussen nicht

zugänglich ist, wie dies Bild 13 zeigt. In den beiden Teilbildern

beträgt die Betriebsspannung des Sensors +12 VDC oder +24 VDC. Die

Steuerung ist, wie es heute üblich ist, TTL-kompatibel, jedoch, weil

meist in HCMOS-Technologie realisiert, sehr hochohmig, wenn noch kein

Pullup- oder Pulldown-Widerstand implemetiert ist. Wir gehen davon aus,

dass dies in Bild 13 der Fall ist. TTL-kompatibel bedeutet, dass der

Eingang auf die definierten Logikpegel an TTL-Ausgängen angepasst ist.

Das bedeutet nicht, dass man keine anern digitalen Signalquellen

anschliessen darf. Sie müssen lediglich die Spannungswerte für logisch

HIGH und LOW einhalten. Im vorliegenden Beispiel ist dies klar gegeben.

In Teilbild 13.1 gehen wir davon aus, dass +Ub nicht stabiliert ist,

weil dies der Sensor auf Grund einer hohen Spannungstoleranz nicht

benötigt. In diesem Fall muss die Spannung im Zustand des HIGH-Pegels am

Eingang der Steuerung mittels einer Zenerdiode mit einer Zenerspannung

von 4.7 V begrenzt werden. Eine Zenerdiode mit 5.1 V könnte schon etwas

zu knapp werden, weil CMOS-Eingänge dürfen nur knapp eine höhere

Spannung haben, als die Betriebsspannung (+5 VDC) beträgt. Damit eine

Zenerdiode vernünftig arbeitet, muss der Z-Strom so gross sein, dass die

Z-Spannung im Sättigungs- und nicht im Knickbereich von Strom und

Spannung liegt. Für kleine 500mW-Zenerdioden liegt dieser Strom im

unteren mA-Bereich. Bei 5 mA beträgt die Verlustleistung bei einer

Z-Spannung von 5 V nur gerade 25 mW. Wenn +Ub = 24 VDC, dann beträgt die

Verlustleistung in R1 120 mW, wenn der Transistor des Sensor

eingeschaltet ist. Bei offenem Transistor ist es weniger. Es genügt ein

kleiner 1/4-Watt-Widerstand für R1 im Wert von 3k9 (+Ub = 24 VDC) oder

1k5 (+Ub = 12 VDC). Wer mehr u.a. über Zenerdioden erfahren möchte,

lese bitte im Elektronik-Minikurs

Z-Diode-Erweiterungskurs und die Bandgap-Referenz.

Die Schaltung in Teilbild 13.2 zeigt eine stabilisierte/geregelte

Betriebsspannung von +Ub = 12 VDC oder +Ub = 24 VDC. In diesem Fall ist

eine Zenerdiode nicht zwingend. Ein Spannungsteiler aus R1 und R2

genügt. Da in beiden Schaltungen ein Querstrom von 5 mA definiert ist,

gelten für R1 die selben Werte für beide Teilbilder. In beiden

Schaltungen liegen beide HIGH-Pegel knapp unterhalb der Betriebsspannung

für die Steuerung von +5 VDC. Diese Dimensionierung ist nur ein

Beispiel. Es kommt immer auch noch darauf an, was das Datenblatt der

Steuerung über die maximale Eingangsspannung und über den

Eingangswiderstand aussagt.

Vielleicht ein Problem beim Einschalten der Steuerung!: Wenn die

Spannung am Eingang der Steuerung um mehr als 0.5 V grösser ist als die

Betriebsspannung und der Eingang ist IC-intern ungenügend oder gar nicht

geschützt, kann es zu einem Latchup-Effekt kommen, der zur Zerstörung

der Eingangsbeschaltung der Steuerung führt. Falls die Steuerung aus

einem einzigen Chip besteht, ist alles defekt. Dies kann dann z.B.

passieren, wenn der Sensor-Transistor offen ist und eine Spannung am

Kollektor anliegt, die einen Stromfluss zum Eingang der Steuerung

ermöglicht und in diesem Zustand die Spannungsversorgung der Steuerung

eingeschaltet wird. Ein Latchup-Effekt lässt sich allerdings mit einem

Vorwiderstand Rv in Serie zum Eingang der Steuerung vermeiden. Der Strom

in den Eingang muss dabei derart reduziert sein, so dass es in der

CMOS-Eingangsstufe sicher keinen Latchup-Effekt auslösen kann. Falls

dieser Eingang jedoch einen Überspannungsschutz zum Zweck enthält den

Latchup-Effekt zu vermeiden, ist Rv (etwa im 10k-Ohm-Bereich)

verzichtbar, ausser es wird, wie bei der HCMOS-Digital-IC-Familie einen

maximalen Eingangsstrom angegeben, der nicht überschritten werden darf.

In diesem Fall muss man sicher stellen, dass +Ub und R1 diesen

Worstcase-Strom nie überschreiten kann. Ist das ohne Rv nicht

gewährleistet, muss man diesen einfügen.

Dieser Stromfluss kommt zustande, wenn die Eingangsspannung um den

Betrag einer Dioden-Schwellenspannung von etwa 0.7 V grösser ist als die

Betriebsspannung (diese kann 0 VDC haben!). Ein zu hoher Strom kann

dabei eine integrierte Schutzschaltung beschädigen oder wenn so eine

nicht vorhanden oder vorhanden und schlecht dimensioniert ist, einen

Latchup-Effekt auslösen. Mehr dazu liest man im Kapitel "Der

Latchup-Effekt" im Elektronik-Minikurs

Der analoge Schalter II

und im letzten Kapitel hier gibt es noch zwei spezielle Links.

Kritik am Titelbild

zu diesem Kapitel:

Dieses kleine Titelbild zeigt gleich zwei Möglichkeiten der

Relaissteuerung. Die Steuerung arbeitet nichtinvertierend, wenn das

Relais (Load-1) im Kollektorkreis des internen Transistors angeschlossen

ist. Im aktiven Zustand (Light = ON) des Sensors ist das Relais

angezogen. Im Zustand der invertierenden Funktion, liegt das Relais

(Load-2) parallel zu Kollektor und Emitter des NPN-Transistors. Das

Relais zieht an im passiven Zustand des Sensors. Der Transistor ist

offen. Von der Betriebsspannung durch den Widerstand

RL und durch das Relais (Load-2) fliesst der Strom

nach GND und das Relais zieht an. Nachteilig an dieser Schaltung ist,

dass die Nennspannung der Relaisspule (Load-2) einen niedrigeren Wert

als die Betriebsspannung der Schaltung haben muss, weil die Relaisspule

nur eine Teilspannung von ihr erhält. RL und

Relaispule arbeiten jetzt als Spannungsteiler. Im ausgeschalteten

Zustand des Relais (Transistor leitend) muss die gesamte

Betriebsspannung über RL liegen und das bedeutet

unnötig hohe Verlustleistung im ausgeschalteten Zustand des Relais. Dies

kann dann zu Problemen führen, wenn ein leistungsstarkes Relais mit

relativ hoher Spulenleistung zum Einsatz kommt.

Dieses Problem wird in den Teilbildern 15.1 und 15.2 getrennt

dargestellt, um es deutlicher hervorzuheben. An Stelle von

RL steht Rv für Vorwiderstand. Gerade bei einer

relativ hohen Betriebsspannung (24 VDC) muss Rv dann viel Leistung

verkraften, wenn das Relais ausgeschaltet ist und so der ganze Strom via

Kollektor-Emitter nach GND fliesst. Teilbild 15.3: Will man diesen Murks

nicht, geht das ganz einfach mit dem zusätzlichen NPN-Transistor T der

das Schalten des Relais übernimmt. Auf diese Weise muss Rv (hier nur als

R bezeichnet) wegen der Stromverstärkung von T nur eine sehr geringe

Leistung verkraften. Die Freilauf-Dioden in den Teilbildern 15.1 und

15.2 zum Schutz des internen Transistors sind für den Einsatz eines

beliebigen Sensors gezeichnet, welche keine internen Schutzmassnahmen

aufweisen.

Betreffs Thema "Schalten mit Transistoren" am Beispiel eines

Schaltmoduls, das der genannte Sensor übrigens auch ist, empfehle ich

den Elektronik-Minikurs

Schalten und Steuern mit Transistoren I.

Zum Schluss: Was ist die Schottky-Diode und was ist ein Latchup-Effekt?

Über Schottky-Dioden liest man etwas in:

Über Latchup-Effekte liest man etwas in:

Der Latchup-Effekt ist auch kurz und informativ in der 11. Auflage (9. Auflage) des Buches HALBLEITERSCHALTUNGSTECHNIK von Tietze/Schenk auf Seite 644 (Seite 215) beschrieben.